From Idea to Implementation

What I really love about my hobby projects is that I can develop answers to questions that I can't explore at work. 20kW HF transmitters, Radar Installations all over the world, and Cutting Edge elemental analysers?No worries.

Digitally Controlled Gain, Isolated PSU Choices? Fergedaboudit.

In part 1, I detailed my path from the concept of a multi-channel volt meter, to a working system based on individual modules. Here I'd like to talk about how I refined the design into my first prototype and then look at where I'm going from there. Like Art, Engineering is never finished, you just chose a point to stop...

Defining Requirements

While building my test modules, I'd pushed optimisation aside, to focus on just proving the concept. Now ready to build my prototype, I'd decided to take stock and think about how I can do this efficiently.

As this was never going to be a CAT-IV design, and was going to be based on what I need in my home workshop, I'd decided that my specs were to set the upper voltage measurement at 50V DC (or AC PEAK) and current limit to 1A. For anything higher, I'll grab a proper multi-meter from the drawer.

Cost is always a driving factor or me, and the price of connectors always amazes me at how fast these can add up. With the above specs in mind, a 3.5mm stereo socket becomes a viable option, and around $1.00 each it's not too pricey. Yes, it's rated to withstand 500V but you would be nuts to use 500V on this type of connector and my PCB clearances will never support those voltages either.

Voltage Sampling

Voltage Input

Choosing the Tip of the 3.mm connector, the voltage is sampled by a resistor divider, with resistors values chosen so that the input impedance is 10Meg (just like most multi-meters) and that the voltage divisor was 100:1 (or 0.01).

You might wonder why I went with 100:1 rather than 10:1 and it's all about compromise. With a downstream gain stage of 2 / 10 / 100, and a Full Scale Deflection (FSD) of 4.096V into my ADC channel, this gives me three useful input voltage ranges of +/- 2V, 20V and a theoretical 200V (but limited to 50).

Note it's +/- 2V and not 0 - 4V with respect to my VGND at the voltage reference, which translates to 0 to 4V at the ADC. Level shifting can mess with your head...

Upper Range

Looking at the input of the ADC, the voltage seen there is the product of the input voltage (Vin) multiplied by the divisor (0.01) and the Gain. The following table illustrates this:

| Vadc (max) | Divisor | Gain | Vin (abs max) |

|---|---|---|---|

| 4.096 | 0.01 | 2 | 102.4 |

| 4.096 | 0.01 | 10 | 20.48 |

| 4.096 | 0.01 | 100 | 2.048 |

Now, to limit the input voltage to safe levels, I've used pair of 5V1 zeners as a back to back clamp. Should the voltage at the junction of R1 and R2 reach around 5V1 the Zeners will conduct and the voltage at TP1 will b limited to around 600mV. The back to back Zeners are to allow positive and negative clamping. The 9M1 resistor keeps currents in the micoramp range should I be dumb enough to hook up to our 230V mains. For safety improvements I should make this two resistors (that sum to 9M1) to keep currents small in case one should fail short circuit.

Lower Range

The ADC I've chose is a 10 bit device. Yes it's not pushing any boundaries on precision here but again it's adequate for my use. As the reference voltage is 4.096V, and 10 bits is 1024 unique codes, each bit represents 4mV as seen by the ADC.

Taking the Gain and divisor stages into account, you can determine the minimum resolution for each gain stage, as per the following table:

| Voltage (max) | Divisor | Gain | Vadc (max) | Counts | Resolution (mV) |

|---|---|---|---|---|---|

| 50 | 0.01 | 2 | 1 | 250 | 200 |

| 20.48 | 0.01 | 10 | 2.048 | 512 | 40 |

| 2.048 | 0.01 | 100 | 2.048 | 512 | 4 |

So the best resolution is 4mV on the 2V range. Again, this isn't going to set any records but is still useful.

Current Sampling

Current Input

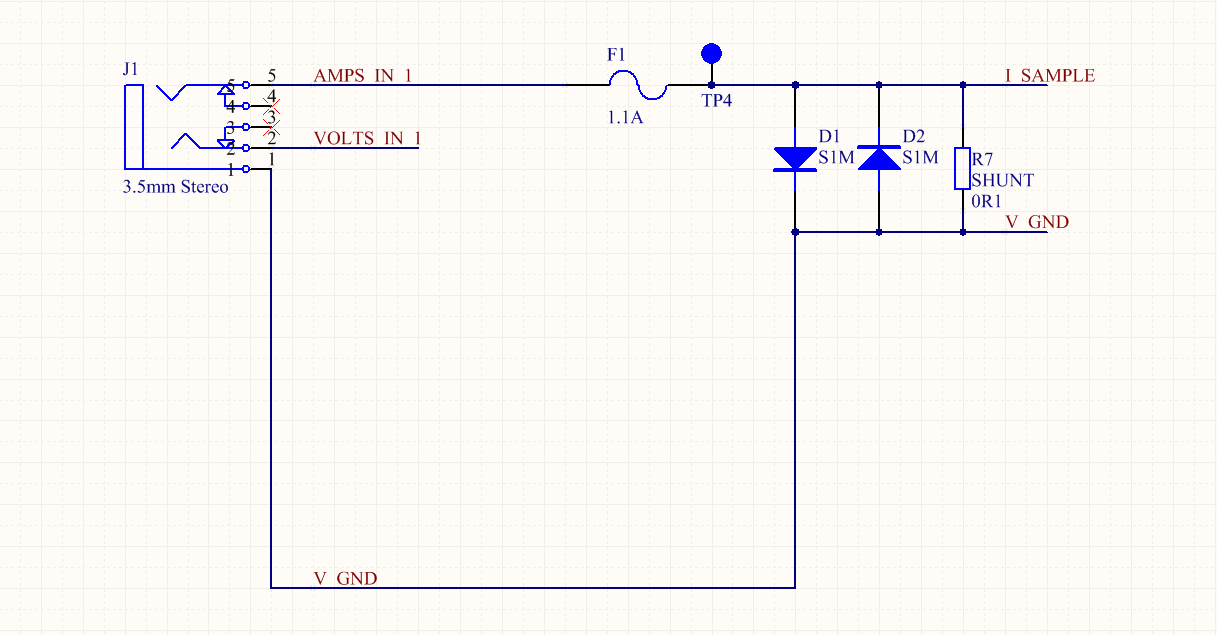

For my current input, I've simply chosen a 0.1 ohm shunt resistor - which is effectively a 10:1 divisor for the sample current. At 1Amp input, 100mV will be seen across this shunt.

To limit input current (in the even of a short circuit to a power rail, for example) I've used a 1.1A polyswitch and a pair of back to back S1M 1A diodes, which are also rated at 1kV Repetitive Reverse Voltage.

Should a test circuit draw more than 1A, the poly switch will kick in a limit current. Should you apply more than 1V to the curent input, the clamp diodes will sink current to Vground and the poly switch again will limit current.

However, the polyswitch I chose is rated to a lousy 8V DC. If you connected the current input to a 12V supply, with only 500mV or so across the diode, the rest of the applied voltage will fall across the polyswitch and rapidly kill it.

I chose 1kV rated diodes in case I again hooked up to 230V so they will survive , but the polyswitch will die a flaming death in that instance. For a final design I'll use a mains rated polyswitch, even if it means moving away from SMD.

| Current (max) | Gain | Vshunt | Vadc (max) | Counts | Resolution (mA) |

|---|---|---|---|---|---|

| 1 | 2 | 0.1 | 0.2 | 50 | 20 |

| 1 | 10 | 0.1 | 1 | 250 | 4 |

| 0.2048 | 100 | 0.02048 | 2.048 | 512 | 0.4 |

My best obtainable resolution is 400uA. Again, useful for the tests I wish to use but again not setting any records.

When considering current meters, it's also useful to look at the burden voltage of the meter. However this is not just due to the losses across the shunt resistor but also the protection fuse or polyswitch. My current polyswitch has a maximum on resistance of 0.18 ohms, so there is nearly 0.3 ohms in series (adding 0.02 for the input socket contacts).

As the same shunt resistor is used for all ranges, the burden voltage for each range remains the same, and can be calculated by:

Burden Voltage = Meter Resistance * measured current

Note that as the burden voltage is a function of the measured current, it is not constant, but i'll just consider the worse case for each range:

| Current (max) | Gain | Resolution (mA) | Burden Voltage |

|---|---|---|---|

| 1 | 2 | 20 | 300mV |

| 1 | 10 | 4 | 300mV |

| 0.2048 | 100 | 0.4 | 61.4mV |

Resolution isn't Accuracy

So far Iv'e been quoting resolution figures, but don't confuse these with accuracy.

For my design there are three factors driving the accuracy:

- The tolerance of the feedback, divider and shunt resistors. My shunt is a 1% tolerance part, but the rest of resistors in my prototype are 5% parts and thus dominate any errors there.

- The voltage reference, which is -8 to plus 6%. More on this later.

- ADC errors, being Integral Error (+/- 1.7 LSB), Offset Error (+/- 2.5 LSB) and Gain Error (+/- 2.0 LSB), which equate to 0.166%, 0.244% and 0.19% respectivley.

To calculate the system accuracy you need to take the square root of the sum of the squares of the errors.

This gives me sqrt( 5^2 + 8^2 + 0.166^2 + 0.244^2 + 0.19^2), for sqrt(89.12), or 9.44%

From above you an see that the errors introduced by the ADC are quite small compared to the resistors and the voltage reference. For a final version I can use 1% resistors (brings error down to 8.07%), and thus the voltage reference is the dominant source of error.

Why the Compromise?

On the surface, the 8% error on the voltage reference seems dreadful, so why am I using it?

Two reasons:

First of all, I'm space constrained so less parts are better. I've chosen the PIC16F1823 for this prototype and in addition to it's 10 bit ADC it also has a built in programmable voltage reference. This chip is a ripper, available for under $2.00, also has a UART and enough IO to control my channel. The cost is the 8% voltage reference.

To improve my circuits accuracy, I could use an external voltage reference with 1% accuracy, but this part alone is nearly $1.00, or half of what the micro costs.

As my goal is for a 'good enough' meter, I'll stick with the internal reference. I also have a plan to calibrate this error (fix it in software!) but I'll look at that later.

Analogue Block Diagram

The internal voltage reference is based on a 1.024V reference, with x2 and x4 multipliers. This allows me to set a 4.096 reference for the ADC and route a 2.048 voltage out a pin and, with an external buffer amplifier, provide a virtual ground for my analogue sampling system.

Add my analogue switching as detailed last time and my system is complete.

Version 2.

As my title suggests, I never get my projects right the first time, and that's okay as I'm doing these to *learn* and you learn from your mistakes.

I also get to look at other options with a re spin of my boards. I'm looking at using the PIC16F1704 as a replacement for the PIC16F1823 - it's pin for pin compatible, and comes with a built in op-amp. It's also cheaper at $1.50 - so I'm saving about $0.80 per channel (op-amp and cheaper micro).

The Vref in the 1704 is also specified at +/-5% so that will also improve system error.

If you're interested, schematics and PCB files for the prototype can be found here.

No comments:

Post a Comment